## Keysight Technologies

W2309EP/ET DDR Bus Simulator and W2317EP/ET DDR Bus Simulator Distributed Computing 8-pack

Data Sheet

## Introduction

The W2309EP/ET double data rate (DDR) Bus Simulator quickly generates accurate bit-error-rate (BER) contours, masks, and margins between the two, for the DDR memory bus specification published by the JEDEC Solid State Technology Association.

The simulator achieves this by use of statistical simulation, meaning no lengthy and time-consuming bit pattern is needed. Instead, it constructs the eye diagram from the transmitter, channel, and receiver impulse responses, and from the stochastic properties of a conceptually infinite non-repeating bit pattern. In doing so, it avoids the pitfalls associated with precarious dual-Dirac extrapolation of a limited bit pattern from either SPICE-like simulation or from convolutional channel simulation.

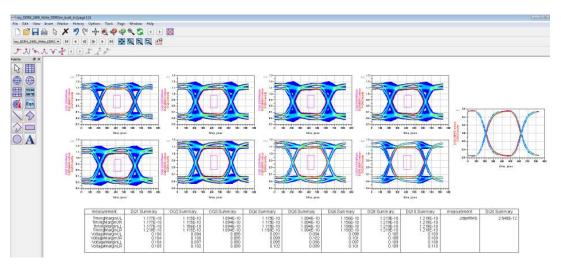

Figure 1. Eye diagrams for a byte lane.

## **Key Features**

- Rigorous DQ and DQS eye calculations to arbitrarily low BER levels

- Built-in driver de-emphasis and receiver continuous-time-linear-equalizer models

- Mix-and-match between built-in, IBIS and circuit models of driver and receiver

- Accounts for crosstalk between signal lines

- Captures asymmetry between rise and fall edges

- Comprehensive margin measurements versus JEDEC DDR4 Rx mask at target BER

- Batch simulation for design space exploration and design of experiments

- Optional parameter sweeps on a compute cluster

## Speed Up Simulation Time

Individual simulations are fast so designers can run in batch mode to quickly explore the design space. An additional product, the W2317EP/ET DDR Bus Simulator Distributed Computing 8-pack, enables you to farm out parameter sweeps to a compute cluster.

Figure 2. DDR batch simulation.

## Rigorous DQ and DQS Eye Calculations

The DDR Bus Simulator offers rigorous DQ (DDR Data Input/Output) and DQS (DDR Data Strobe) eye calculations to arbitrarily low BER levels, including the 1E-16 contour specified by JEDEC, accounting for crosstalk and for asymmetry between rising and falling transition times. It provides comprehensive timing and voltage margins between the selected BER contour and the DDR4 receive mask specification.

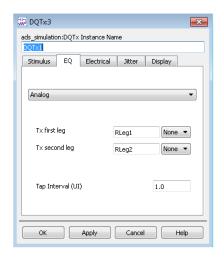

Figure 3. The built-in transmitter includes an optional pre-emphasis.

# Mix-and-Match between Built-in, IBIS and Circuit Models

The product allows for three IC model types: built-in, Input/output Buffer Information Specification (IBIS), or circuit models. The built-in driver and receiver model de-emphasis and continuous-time linear equalization (CTLE), respectively. Designers can "mix-and-match" model types in their schematic.

Figure 4. The built-in receiver includes CTLE capability.

#### myKeysight

#### myKeysight

#### www.keysight.com/find/mykeysight

A personalized view into the information most relevant to you.

www.keysight.com/find/eesof

For more information on Keysight Technologies' products, applications or services, please contact your local Keysight office. The complete list is available at: www.keysight.com/find/contactus

#### Americas

| Canada        | (877) 894 4414   |

|---------------|------------------|

| Brazil        | 55 11 3351 7010  |

| Mexico        | 001 800 254 2440 |

| United States | (800) 829 4444   |

#### Asia Pacific

| Australia          | 1 800 629 485  |

|--------------------|----------------|

| China              | 800 810 0189   |

| Hong Kong          | 800 938 693    |

| India              | 1 800 112 929  |

| Japan              | 0120 (421) 345 |

| Korea              | 080 769 0800   |

| Malaysia           | 1 800 888 848  |

| Singapore          | 1 800 375 8100 |

| Taiwan             | 0800 047 866   |

| Other AP Countries | (65) 6375 8100 |

|                    |                |

#### Europe & Middle East

Opt. 2 (FR) Opt. 3 (IT)

0800 0260637

For other unlisted countries: www.keysight.com/find/contactus (BP-09-23-14)

United Kingdom